3 can be used to implement a 64-bit shift register in 6-input LUT 400.

The same shift control circuit illustrated in FIG. Other solutions for the 6-input LUT shift register, which may be more costly in terms of layout area, include the following. Does each 6-input LUT compare 2 pairs of 3-bits, or do two LUT's compare 12-bits, etc. The additional cost in moving from the 4-input LUT to the 6-input LUT is therefore reduced. If you do not add the parentheses, the synthesis tool may partition the addition in a way that is not optimal for the architecture. 6-Input LUT and logic functions Just would like some clarification on how big comparisons pan out with the 6-input LUT.

6 input lut 64 bits#

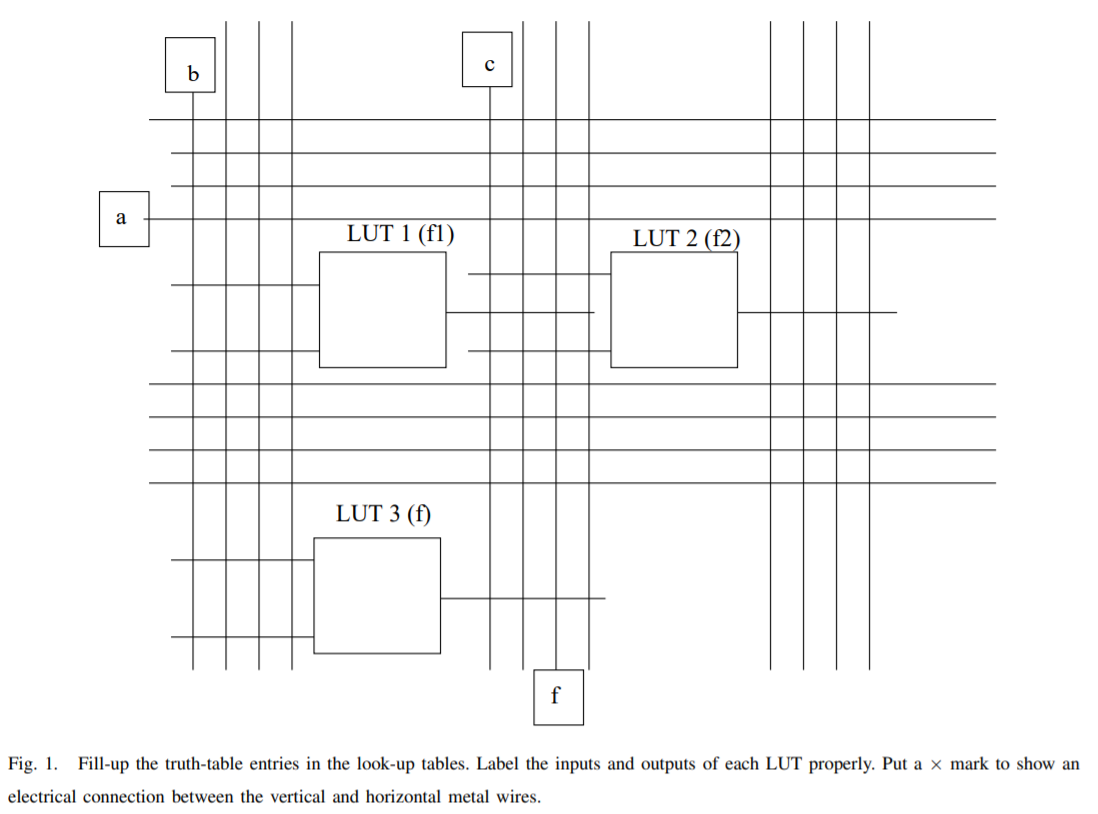

For example, depending on your synthesis tool, the HDL code sum = (A + B + C) + (D + E) is more likely to create the optimal implementation of a 3-input adder for A + B + C followed by a 3-input adder for sum1 + D + E than the code without the parentheses. The Xilinx 6-input LUT is a look-up table with a total of 64 bits of logic programming space and 6 independent inputs. If your design is not pipelined, a ternary tree provides much better performance than a binary tree.

In later technologies, which use the 6-input LUT, they use the multiplier 1.6. The example shows a pipelined adder, but partitioning your addition operations can help you achieve better results in non-pipelined adders as well. In older Xilinx technologies (with 4-input LUTs) they used to use 1.25 as the multiplier to get from LUTs to Logic Cells, since the Xilinx slice also had the carry chain and wide MUX, which made it possible to do more than a simple 4-input LUT would be able to do.

0 kommentar(er)

0 kommentar(er)